## Battery Management System applied to Projecto FST's EV prototype

Bruno Manuel Baraças dos Santos

# Thesis to obtain the Master of Science Degree in Aerospace Engineering

Supervisors: Prof. Dr. Rui Manuel Rodrigues Rocha Prof. Dr. Moisés Simões Piedade

### Examination Committee

Chairperson: Prof. Dr. João Manuel Lage de Miranda Lemos Supervisor: Prof. Dr. Rui Manuel Rodrigues Rocha Member of the Committee: Prof. Dr. António Joaquim dos Santos Romão Serralheiro

October 2014

# Agradecimentos / Acknowledgments

Devo uma palavra de agradecimento, em primeiro lugar, aos professores que me orientaram. O professor Moisés Piedade cuja orientação começou bem antes deste projecto e ao professor Rui Rocha que tantas vezes deu uma nova perspectiva e me obrigou a pensar em novos problemas. Aos dois um obrigado.

Ao Daniel Pinho, Pedro Oliveira, Miguel Silva, Rui Andrade e Miguel Guedes, tenho a agradecer o seu envolvimento directo nos BMSs originais que precederam e tanto acrescentaram ao aqui proposto. Agradeço também ao Pedro Costa e à Mariana Cunha, em particular, pela enorme ajuda na recuperação da bateria e pelo empenho em trabalhar nas soluções futuras aqui apresentadas. E, com receio de excluir alguém, agradeço a todos os restantes membros do Projecto FST pelo trabalho em torno de um objectivo comum sem o qual não poderia existir esta tese.

Finalmente, agradeço a todos os que através da sua constante amizade e amor me motivaram e suportaram ao longo de mais esta jornada e que tantas vezes suportaram a minha ausência.

Last but not least, a thank you note in English to fellow Formula Student teams *StarkStrom Augsburg e.V.*, *AMZ Racing* and *ETSEIB Motorsport*. Specifically, Robert Dollinger, Fabio Widmer and Guifré Vendrell respectively, for the contributions that enriched this work.

ii

### Resumo

Esta tese tem como objectivo projectar, construir e testar um novo Sistema de Gestão de Baterias (BMS) para os protótipos mais recentes do Projecto Formula Student Técnico (Projecto FST), em particular o actual *FST-05e* e o futuro *FST-06e*. O novo sistema deve responder a alterações chave na tecnologia empregue pela equipa Projecto FST em sintonia com os regulamentos aplicáveis da competição de Formula Student (FS).

Para cada um dos protótipos mencionados, a equipa desenvolveu / está a desenvolver um Veículo Eléctrico (EV) com uma bateria de 600 V composta por células de lítio tipo pouch, mas com configurações potencialmente diferentes — dependente da capacidade das células escolhidas e outras especificações do carro como a geometria da bateria. Com um sistema tão delicado como este, o sistema BMS requer fiabilidade e segurança em condições de operação bastante ruidosas e com bastante vibração como é o caso de um veículo, e mais ainda devido à natureza de competição do projecto. Ao mesmo tempo, o sistema deve ainda obedecer a um orçamento limitado, satisfazer os constrangimentos de espaço (e peso) e disponibilizar todas as interfaces apropriadas.

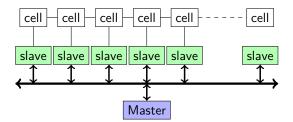

A solução proposta consiste num BMS híbrido com características de sistema distribuído e modular composto por um módulo mestre e vários módulos escravos que comunicam através de um barramento Controller Area Network (CAN). O sistema possibilita ainda a existência de vários contentores de baterias, podendo por isso haver mais do que um módulo mestre no sistema completo.

**Keywords:** Sistema de Gestão de Baterias, Vehículo Eléctrico, Segurança de Baterias, Baterias de Lítio, Formula Student

### Abstract

This thesis has the purpose of designing, building and testing a new Battery Management System (BMS) for the recent electric prototypes designed by Projecto Formula Student Técnico (Projecto FST), in particular the current *FST-05e* and the future *FST-06e*. The new design should accommodate core changes in the technology used by the Projecto FST team in accordance with the applicable rules from the Formula Student (FS) competition.

In both mentioned prototypes, the team developed / is developing a battery powered Electric Vehicle (EV) with a 600 V battery of pouch lithium cells, but potentially different configurations — dependent on cell capacity and other car specifications like battery geometry. With such a sensitive system, the BMS needs to be very reliable and safe, even in a noisy environment and subject to vibrations as is the case of a vehicle, even more due to the competition nature of the project. At the same time, the system should still fit the budget of the team as well as comply with space (and weight) limits and provide all the appropriate interfaces.

The solution presented here is a hybrid BMS with modular and distributed features composed by one master module and several slave modules communicating through a Controller Area Network (CAN) bus. This system also allows for more than one battery container, therefore more than one master module may be present in the complete system.

**Keywords:** Battery Management System, Electrical Vehicle, Battery Safety, Lithium Battery, Formula Student

# Contents

| A  | grade  | ciment   | os / Ack    | nowledgme    | nts     |      |      |      |      |      |       |      |       |   | i    |

|----|--------|----------|-------------|--------------|---------|------|------|------|------|------|-------|------|-------|---|------|

| Re | esume  | D        |             |              |         |      |      |      |      |      |       |      |       |   | iii  |

| AI | bstrad | ct       |             |              |         |      |      |      |      |      |       |      |       |   | v    |

| Co | onten  | ts       |             |              |         |      |      |      |      |      |       |      |       |   | vii  |

| Li | st of  | Figures  | 6           |              |         |      |      |      |      |      |       |      |       |   | xi   |

| Li | st of  | Tables   |             |              |         |      |      |      |      |      |       |      |       | : | xiii |

| AI | brevia | itions   |             |              |         |      |      |      |      |      |       |      |       |   | xv   |

| Sy | /mbol  | s        |             |              |         |      |      |      |      |      |       |      |       | > | vii  |

| 1  | Intr   | oductio  | on          |              |         |      |      |      |      |      |       |      |       |   | 1    |

|    | 1.1    | Motiv    | ation       |              |         | <br> | <br> | <br> | <br> | <br> |       | <br> | <br>- |   | 2    |

|    | 1.2    | Projec   | t scope ai  | nd objective |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 3    |

|    | 1.3    | Syster   | n definitio | n            |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 4    |

|    | 1.4    | Struct   | ure of the  | thesis       |         | <br> | <br> | <br> | <br> | <br> | <br>- | <br> | <br>- | • | 4    |

| 2  | Stat   | te of th | ie art      |              |         |      |      |      |      |      |       |      |       |   | 7    |

|    | 2.1    | Batter   | y technolo  | ogy          |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 7    |

|    | 2.2    | BMS f    | features    |              |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 9    |

|    |        | 2.2.1    | Cell bala   | incing       |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 9    |

|    |        |          | 2.2.1.1     | Passive ba   | lancing | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 11   |

|    |        |          | 2.2.1.2     | Active bala  | ancing  | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 11   |

|    |        | 2.2.2    | Perform     | ance parame  | ters    | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 13   |

|    |        |          | 2.2.2.1     | SoC and D    | 00D     | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 13   |

|    |        |          | 2.2.2.2     | SoH          |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 14   |

|    | 2.3    | BMS t    | topology    |              |         | <br> | <br> | <br> | <br> | <br> |       | <br> |       |   | 16   |

|   |      | 2.3.1   | Centralized                           | 16 |

|---|------|---------|---------------------------------------|----|

|   |      | 2.3.2   | Distributed                           | 17 |

|   |      | 2.3.3   | Modular                               | 17 |

|   | 2.4  | BMS ir  | n Formula Student                     | 18 |

| 3 | Syst | em arcl | hitecture                             | 21 |

|   | 3.1  | System  | definition                            | 21 |

|   |      | 3.1.1   | FST-05e                               | 22 |

|   |      |         | 3.1.1.1 Battery design                | 22 |

|   |      |         | 3.1.1.2 BMS design                    | 26 |

|   |      |         | 3.1.1.3 Implementation and deployment | 27 |

|   |      | 3.1.2   | FST-06e                               | 27 |

|   | 3.2  | BMS a   | rchitecture                           | 28 |

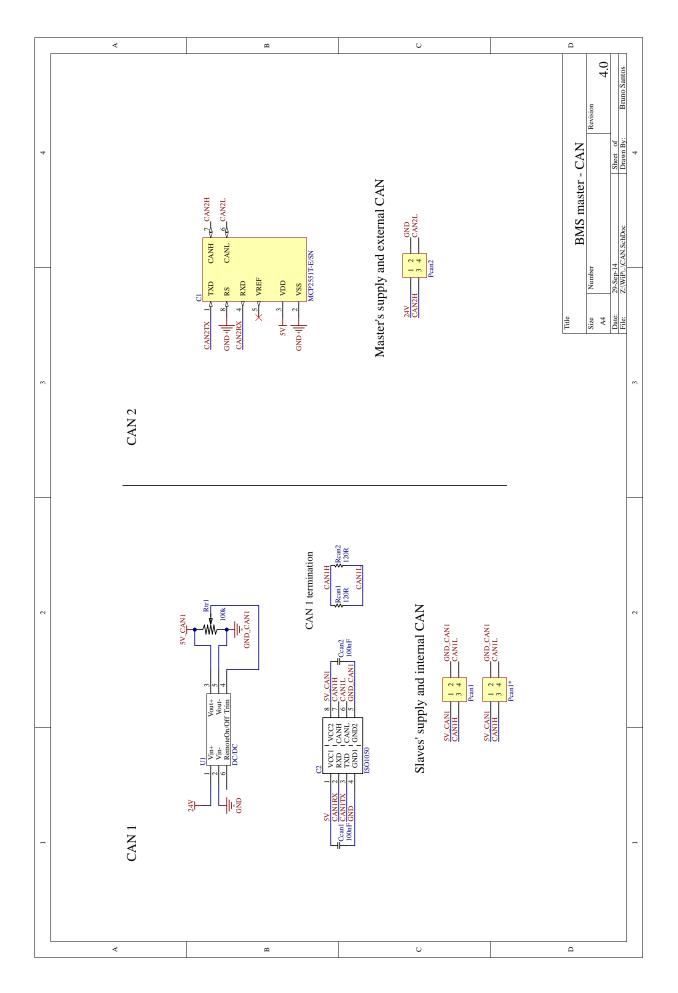

|   | 3.3  | Comm    | unications                            | 30 |

|   | 3.4  | Integra | tion within the vehicle               | 31 |

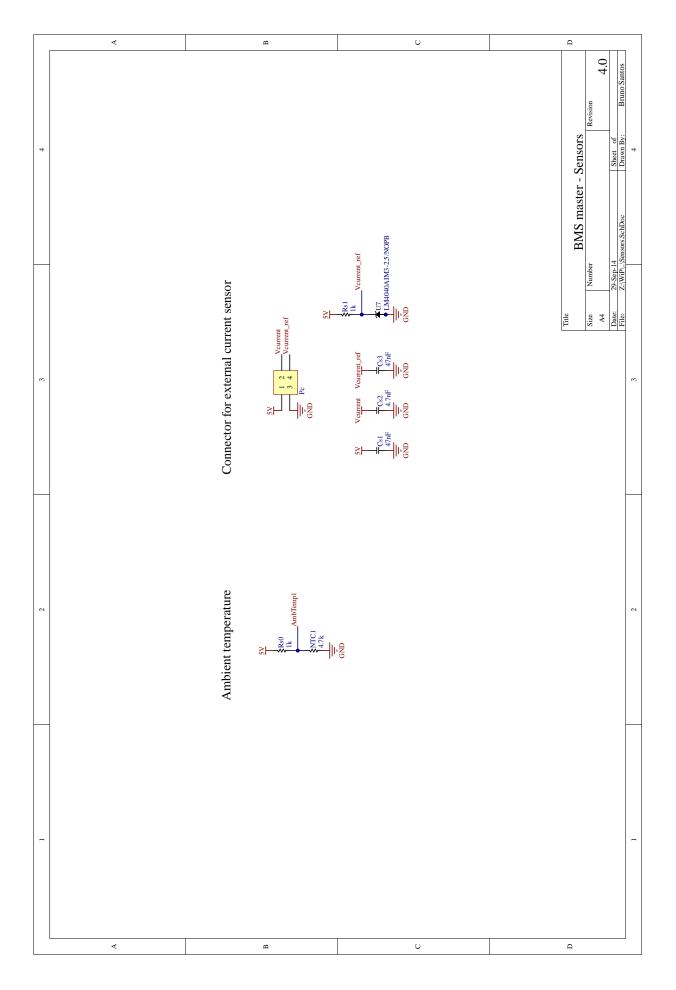

|   | 3.5  | Cell mo | onitoring                             | 32 |

|   |      | 3.5.1   | Voltage                               | 33 |

|   |      | 3.5.2   | Temperature                           | 34 |

|   |      | 3.5.3   | Current                               | 34 |

|   | 3.6  | Safety  | systems                               | 35 |

|   |      | 3.6.1   | AIRs                                  | 35 |

|   |      | 3.6.2   | Pre-charge and discharge circuits     | 35 |

|   | 3.7  | Cell ba | lancing                               | 36 |

|   |      | 3.7.1   | Balance method                        | 36 |

|   |      | 3.7.2   | Balance current                       | 37 |

|   | 3.8  | Battery | y interface                           | 38 |

| 4 | Slav | e modu  | ıle                                   | 41 |

|   | 4.1  |         | ecture                                | 41 |

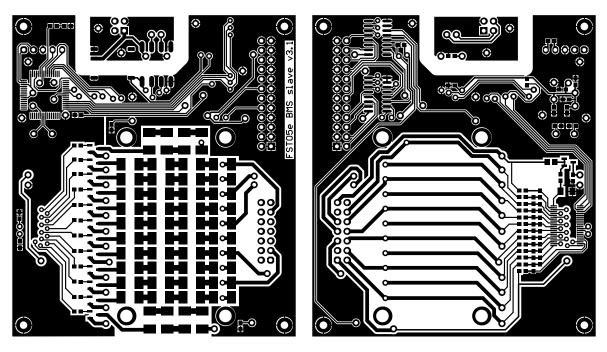

|   |      | 4.1.1   | Layout                                | 42 |

|   |      | 4.1.2   | Routines                              | 42 |

|   | 4.2  | Voltage | e monitoring                          | 44 |

|   |      | 4.2.1   | Measurements                          | 46 |

|   |      | 4.2.2   | Self-checks                           | 47 |

|   | 4.3  |         | rature monitoring                     | 48 |

|   | -    | 4.3.1   | Measurements                          | 49 |

|   |      | 4.3.2   | Self-checks                           | 49 |

|     | 4.4    | Balancing                        | . 50 |

|-----|--------|----------------------------------|------|

|     |        | 4.4.1 Strategy                   | . 51 |

|     |        | 4.4.2 Exceptions                 | . 53 |

|     | 4.5    | SoC estimation                   | . 53 |

| 5   | Mas    | ster module                      | 55   |

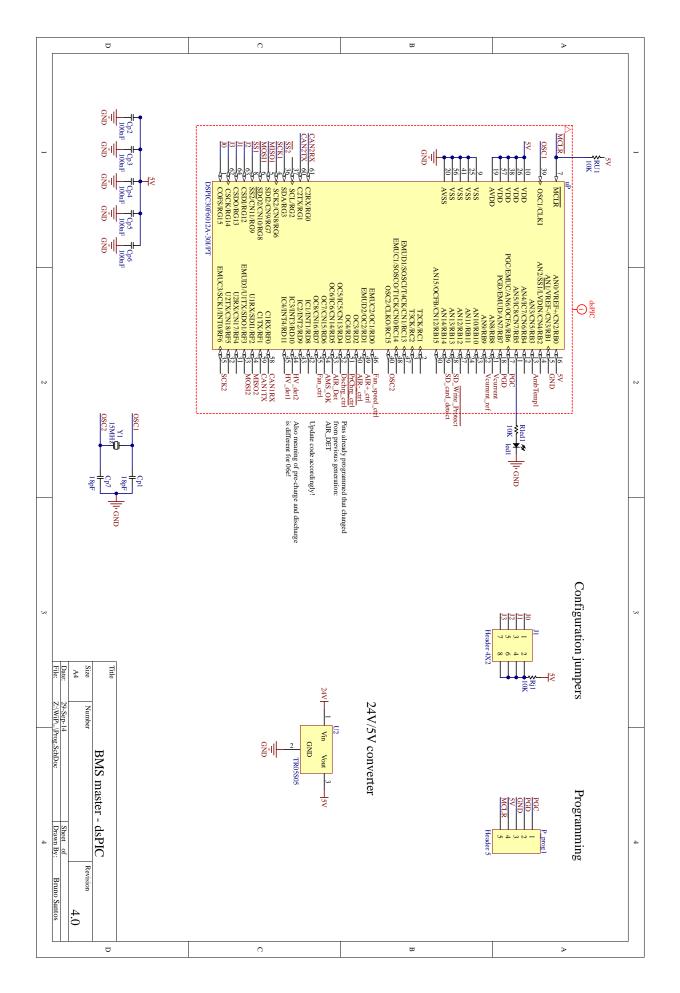

|     | 5.1    | Architecture                     | . 55 |

|     |        | 5.1.1 Layout                     | . 57 |

|     |        | 5.1.2 Routines                   | . 57 |

|     |        | 5.1.3 Master-slave coordination  | . 59 |

|     |        | 5.1.4 Master-master coordination | . 59 |

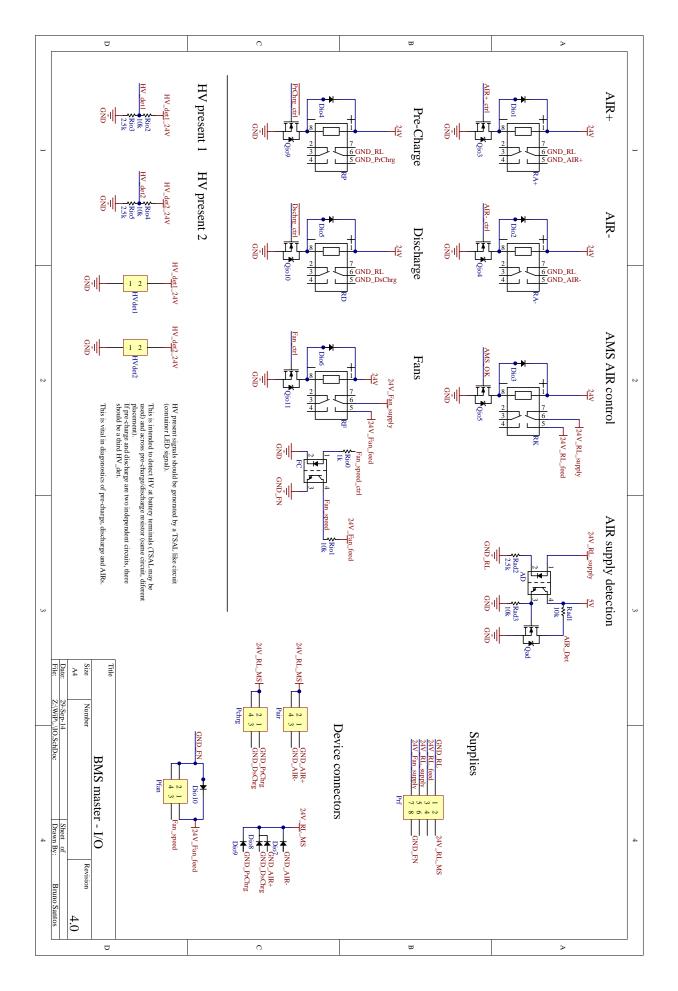

|     | 5.2    | Tractive system control          | . 60 |

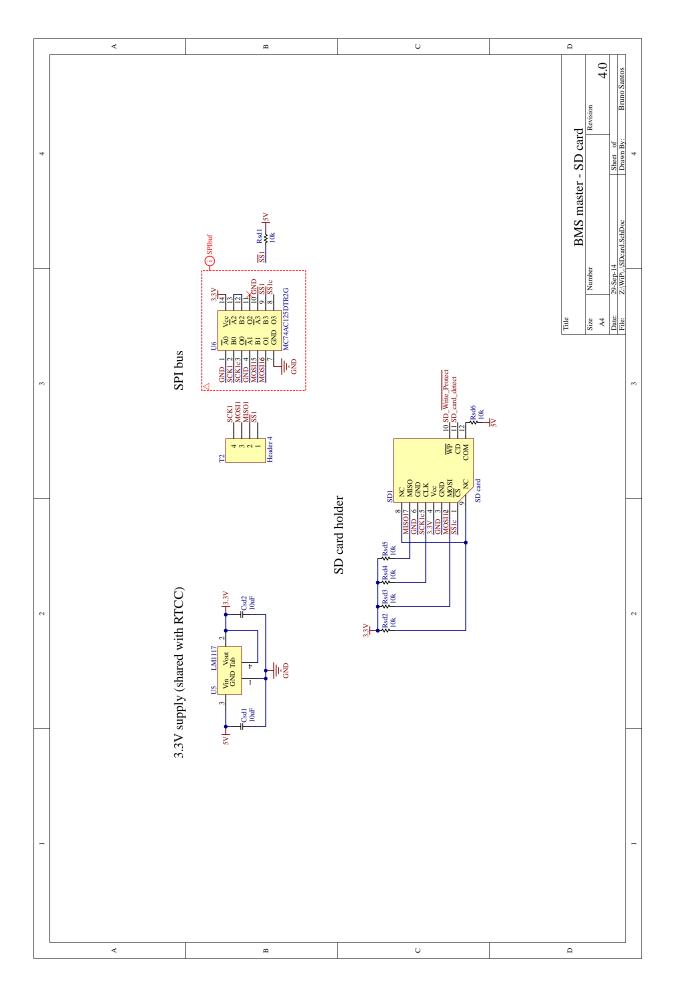

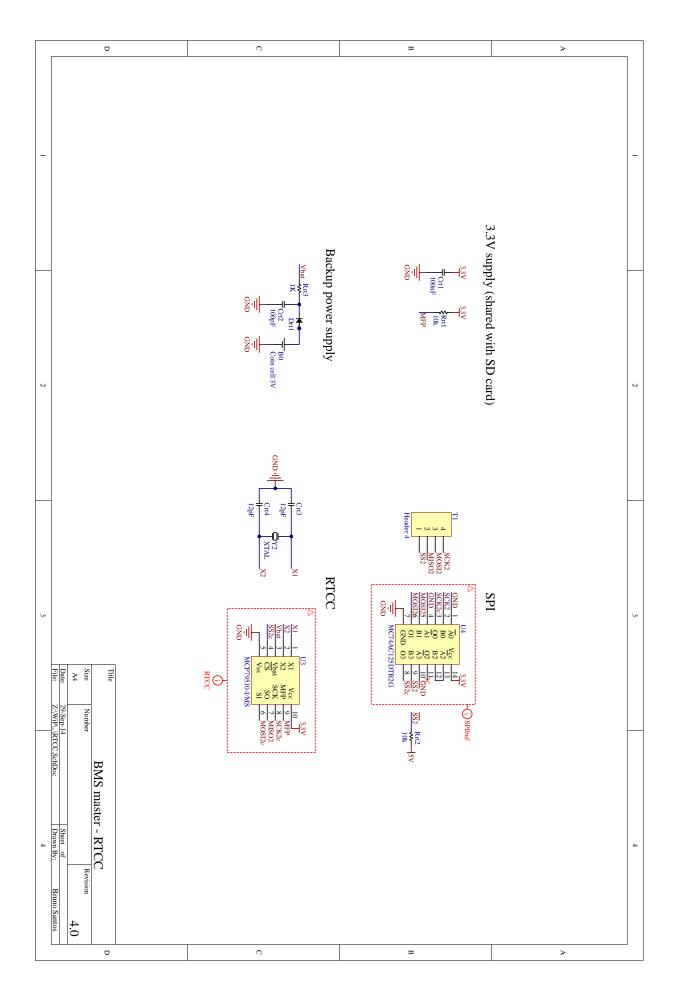

|     | 5.3    | Data storage                     | . 61 |

|     | 5.4    | Current intensity                | . 62 |

|     | 5.5    | Charging                         | . 62 |

| 6   | CAN    | N tools                          | 63   |

|     | 6.1    | CAN-USB translator               | . 64 |

|     | 6.2    | FST CAN interface                | . 65 |

|     |        | 6.2.1 Console module             | . 65 |

|     |        | 6.2.2 Battery module             | . 66 |

| 7   | Test   | ts and deployment                | 69   |

|     | 7.1    | Tests and development            | . 69 |

|     |        | 7.1.1 Design validation          | . 71 |

|     | 7.2    | Deployment                       | . 73 |

|     |        | 7.2.1 Charging                   |      |

|     |        | 7.2.2 Discharging                | . 76 |

|     | 7.3    | Cost analysis                    | . 77 |

| 8   | Con    | nclusions                        | 79   |

|     | 8.1    | Future work                      | . 80 |

| Re  | eferen | ncos                             | 81   |

| ive | aeren  |                                  | 01   |

| Α   | BMS    | IS Parameters                    | 83   |

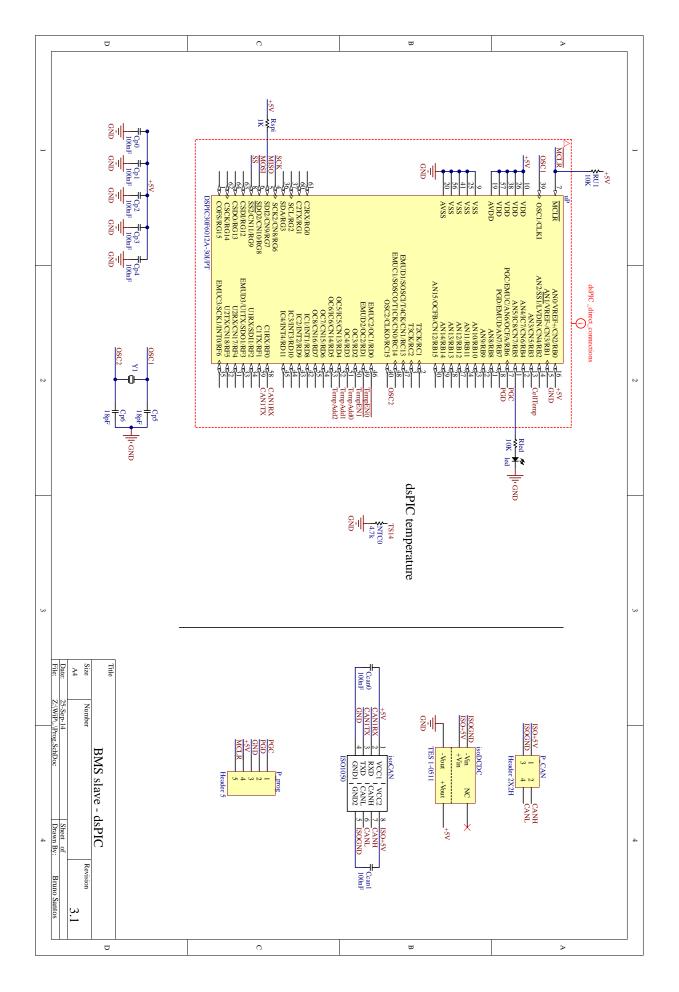

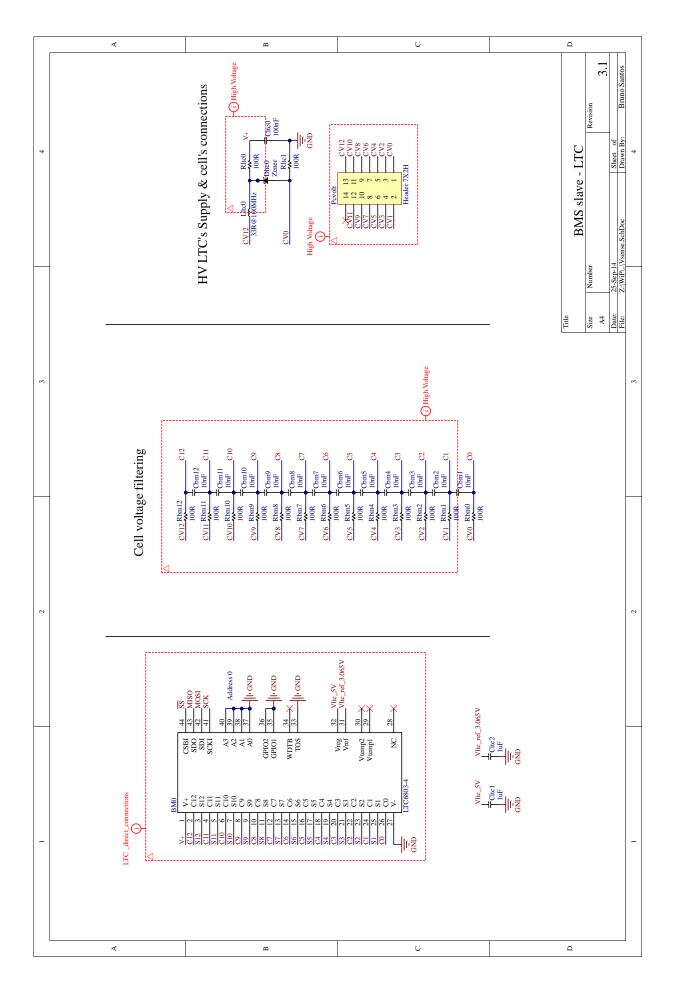

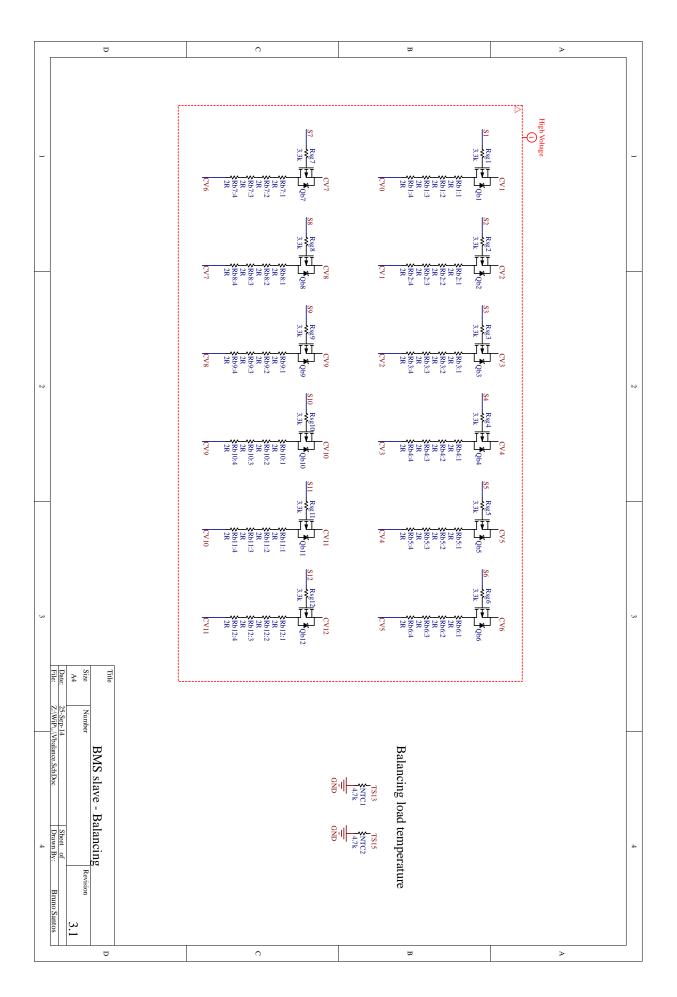

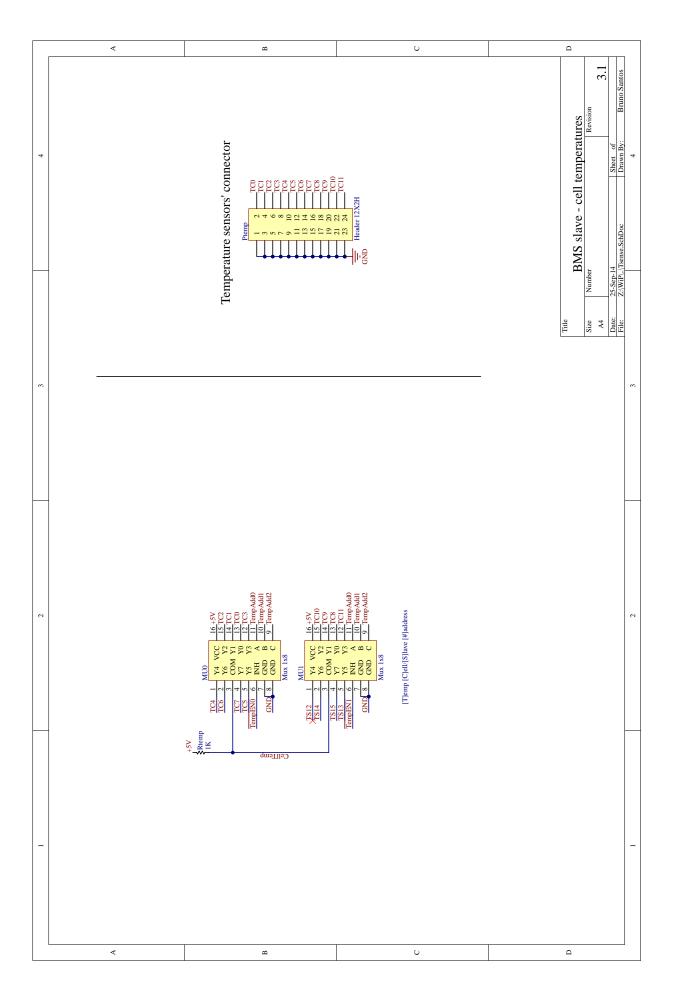

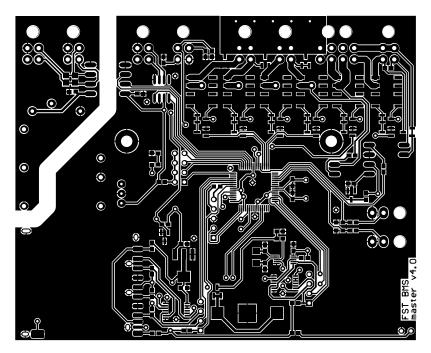

| В   | Slav   | ve module v3.1 schematics        | 85   |

| с   | Slav   | ve module v3.1 masks             | 91   |

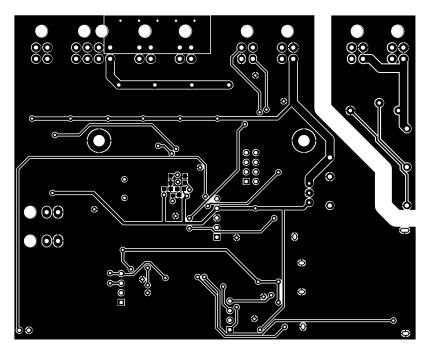

- D Master module v4.0 schematics

- E Master module v4.0 masks

93

# **List of Figures**

| 1.1 | <i>FST-05e</i> and team in Germany 2013. [Courtesy of Projecto FST]                                                                      | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | FST-06e render for Class 2 competition in Silverstone 2014. [Courtesy of Projecto FST]                                                   | 3  |

| 2.1 | Two types of lithium-ion cells. Not to scale                                                                                             | 8  |

| 2.2 | Example of an unbalanced array of cells                                                                                                  | 10 |

| 2.3 | Discharge rate characteristics for Lithium-Ion Polymer (LiPO) cells EPS4500XP, used in <i>FST-05e</i> .<br>[E Propulsion Systems, 2012]  | 14 |

| 2.4 | Centralized BMS.                                                                                                                         | 16 |

| 2.5 | Distributed BMS.                                                                                                                         | 17 |

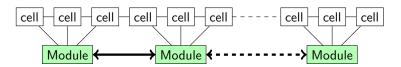

| 2.6 | Modular BMS                                                                                                                              | 18 |

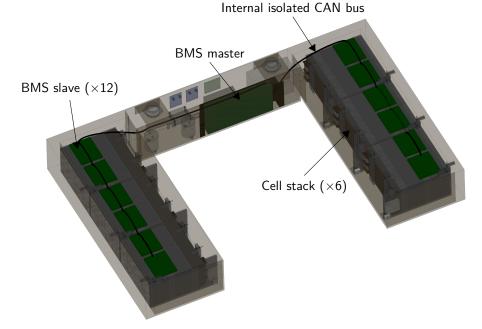

| 3.1 | Render from the design phase of FST-05e's battery. [Adapted from Projecto FST [2013a]]                                                   | 23 |

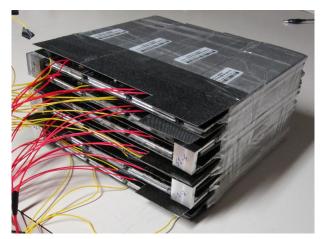

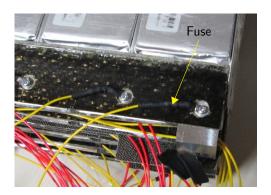

| 3.2 | Cell stack from <i>FST-05e</i> . [Projecto FST, 2013 <i>a</i> ]                                                                          | 24 |

| 3.3 | Analysis of connections between cells and BMS for <i>FST-05e</i> . For simplicity, the schematic illustrates a differential measurement. | 24 |

| 3.4 | Original slave module for FST-05e (v2.1)                                                                                                 | 26 |

| 3.5 | Preliminary render of right hand side battery of FST-06e. [Courtesy of Projecto FST]                                                     | 28 |

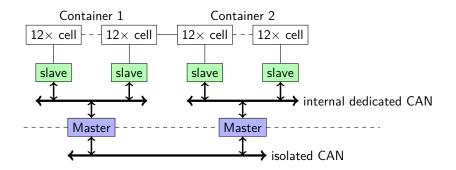

| 3.6 | Proposed topology for new BMS in a two container configuration.                                                                          | 30 |

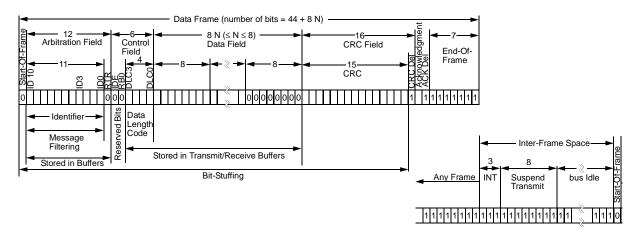

| 3.7 | Standard CAN frame. [Microchip, 2006]                                                                                                    | 31 |

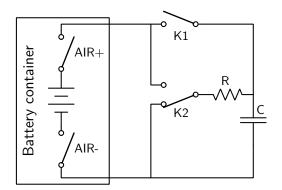

| 3.8 | Pre-charge and discharge circuit. All switches represent relays controlled by the master module.                                         | 35 |

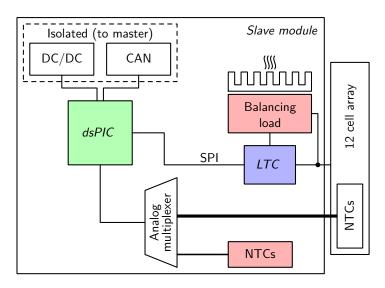

| 4.1 | Slave module architecture ( <i>FST-05e</i> )                                                                                             | 42 |

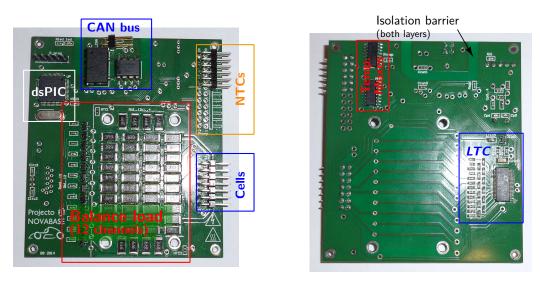

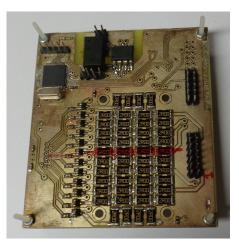

| 4.2 | Slave module v3.1 ( <i>FST-05e</i> )                                                                                                     | 43 |

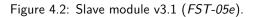

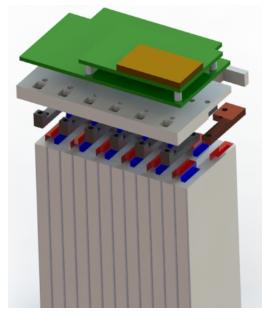

| 4.3 | <i>FST-06e</i> stack concept. [Courtesy of Projecto FST]                                                                                 | 43 |

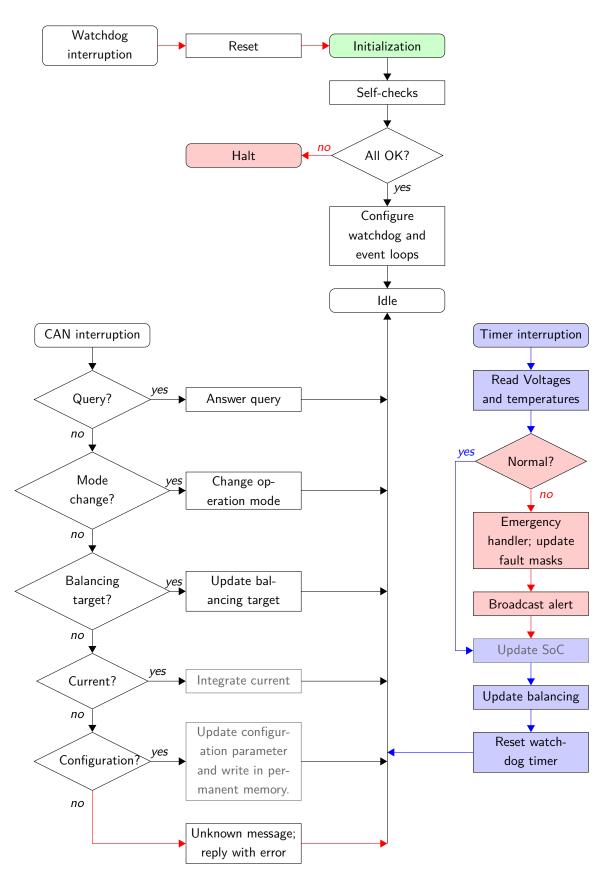

| 4.4 | Simplified slave module flowchart.                                                                                                       | 45 |

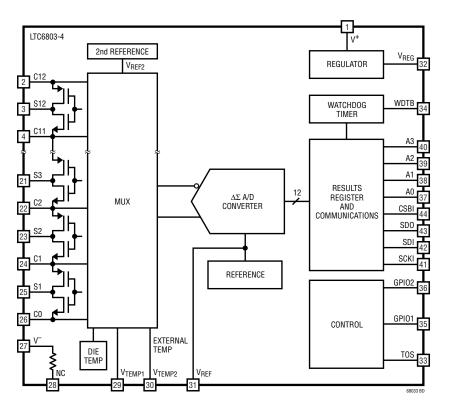

| 4.5 | LTC internal architecture. [Linear Technology, 2011]                                                                                     | 46 |

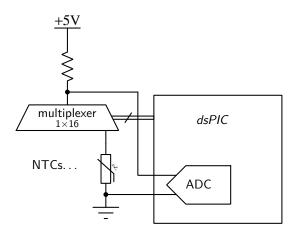

| 4.6 | Negative Temperature Coefficient thermistors (NTCs) multiplexing schematic                                                               | 48 |

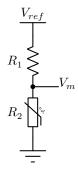

| 4.7 | NTC resistance $(R_2)$ measuring schematic through a voltage divider                                                                     | 49 |

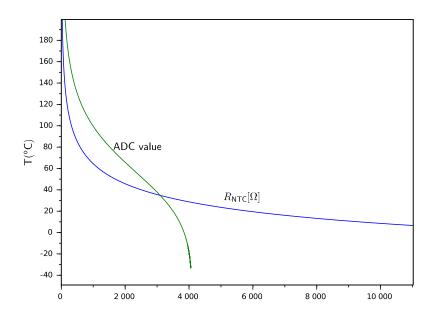

| 4.8 | Measured temperature relative to NTC resistance and Analogue-Digital Converter (ADC) value.                                              | 50 |

| 4.9 | Slave module v3.1 ( <i>FST-05e</i> ) fitted with a low profile heat sink                                                                 | 52 |

| 4.10 | State of Charge (SoC) mapping of voltage measurements for cells $EPS4500XP$ ( $FST-05e$ )                                                                                                  | 54 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

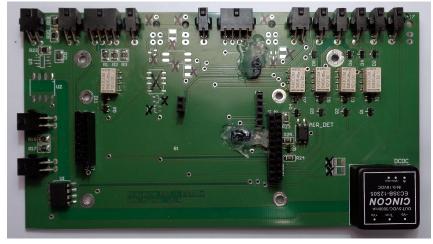

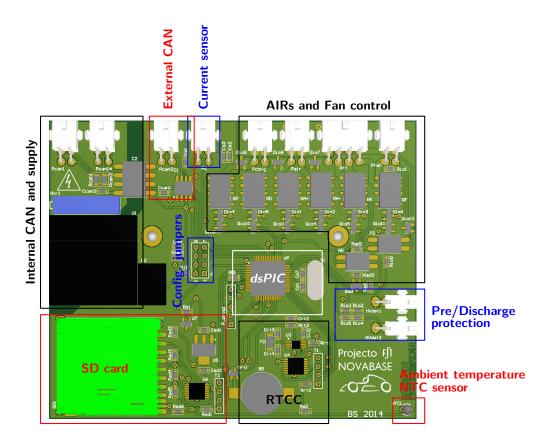

| 5.1  | Original master module (v3.4) components                                                                                                                                                   | 56 |

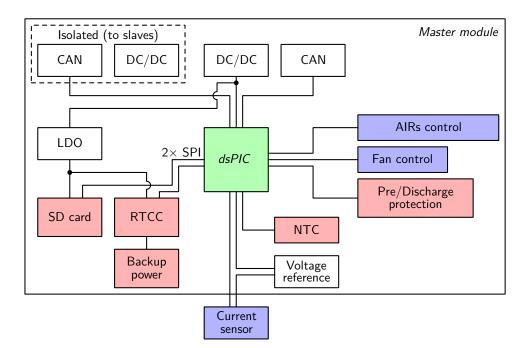

| 5.2  | Master module architecture.                                                                                                                                                                | 57 |

| 5.3  | Render of master module v4.0.                                                                                                                                                              | 58 |

| 6.1  | Translator module. Left connector connects to CAN and the right one to Universal Serial Bus (USB); Light Emitting Devices (LEDs) indicate bus activity.                                    | 64 |

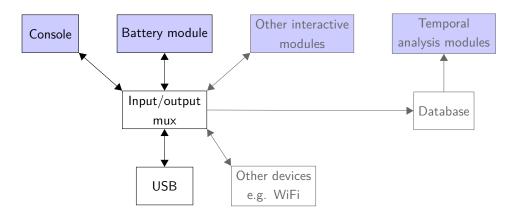

| 6.2  | $FST\ CAN\ interface\ architecture.$ Blue blocks correspond to Graphical User Interface (GUI) interfaces. Grayed out blocks represent features not implemented nor covered in this thesis. | 66 |

| 6.3  | Console tab.                                                                                                                                                                               | 66 |

| 6.4  | Battery tab. Battery offline.                                                                                                                                                              | 67 |

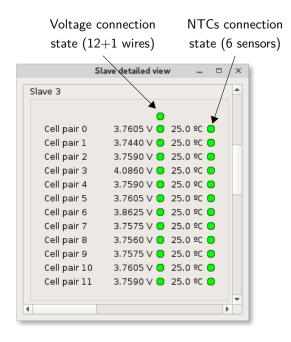

| 6.5  | Example of detailed information for slave 3 under normal conditions                                                                                                                        | 67 |

| 6.6  | Battery detail window.                                                                                                                                                                     | 68 |

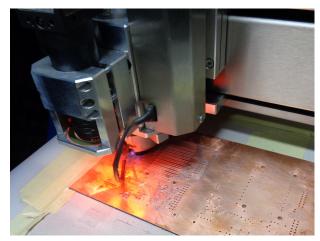

| 7.1  | Prototype slave v3.0.                                                                                                                                                                      | 70 |

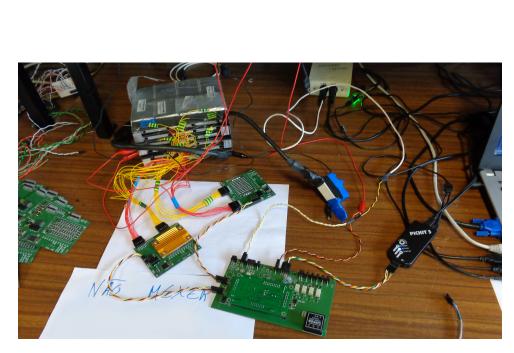

| 7.2  | Master v3.4 and slave v3.1 integration tests                                                                                                                                               | 70 |

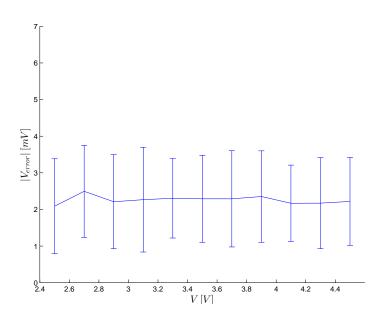

| 7.3  | Results of voltage characterization of all produced slaves. Out of 20 slaves plus the prototype, one was damaged before characterization and 3 were never soldered                         | 72 |

| 7.4  | FST-05e battery.                                                                                                                                                                           | 74 |

| 7.5  | Cell voltages in a final stage of balancing. Green 'lights' indicate good connections to cells and sensors.                                                                                | 75 |

| 7.6  | Battery interface showing battery under charging conditions.                                                                                                                               | 76 |

| 7.7  | Manuel Ferreira driving <i>FST-05e</i> in endurance event, Silverstone, <i>FSUK2014</i> . [Courtesy of Projecto FST]                                                                       | 77 |

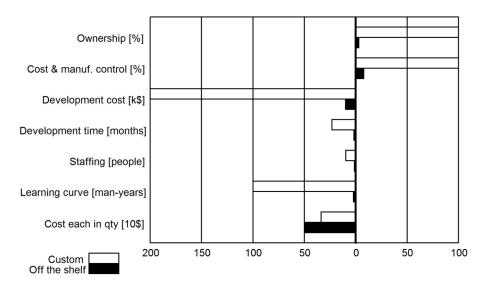

| 7.8  | Comparison of commercial (off the shelf) and custom BMSs. [Andrea, 2010]                                                                                                                   | 78 |

# **List of Tables**

| 2.1 | Distinction between BMS types; red column only applies to digital BMSs                                                     | 9  |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of active balancing strategies in usual topologies. Actual implementations intro-<br>duce some variations tough | 12 |

| 2.3 | SoC and Depth of Discharge (DoD) estimation methods for lithium-ion cells. [Piller et al., 2001; Pop et al., 2008]         | 15 |

| 2.4 | Sample of BMSs used in electric FS cars. [Courtesy of AMZ Racing, Starktrom Augsburg e.V. and ETSEIB Motorsport]           | 19 |

| 3.1 | FST-05e battery specifications.                                                                                            | 22 |

| 3.2 | FST-06e battery specifications.                                                                                            | 28 |

| 3.3 | Measurement limits                                                                                                         | 33 |

| 7.1 | Characterization summary. These values apply to $ V_{error} $ as in figure 7.3                                             | 72 |

# **Abbreviations**

| Analogue-Digital Converter                          |

|-----------------------------------------------------|

| Accumulator Insulator Relay                         |

|                                                     |

| American Standard Code for Information Interchange  |

| Basalt Fiber Reinforced Plastic                     |

| Battery Management System                           |

|                                                     |

| Computer Assisted Design                            |

| Controller Area Network                             |

| Closed Circuit Voltage                              |

| Carbon Fiber Reinforced Plastic                     |

| Cyclic Redundancy Check                             |

|                                                     |

| Direct current                                      |

| Direct current (DC) to DC converter                 |

| Data Length Code                                    |

| Depth of Discharge                                  |

|                                                     |

| Electrically Erasable Programmable Read Only Memory |

| Electromagnetic Interference                        |

| Electric Vehicle                                    |

| Formula Student                                     |

| Formula Society of Automotive Engineers (SAE)       |

| · · · · · · · · · · · · · · · · · · ·               |

| Grounded Low Voltage System                         |

| GNU is Not Unix                                     |

| Graphical User Interface                            |

|                                                     |

| Input/Output                                        |

| Inter-Integrated Circuit                            |

|                                                     |

| IC                                                                       | Integrated Circuit                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID                                                                       | Identifier                                                                                                                                                                                                                                                           |

| IMechE                                                                   | Institution of Mechanical Engineers                                                                                                                                                                                                                                  |

| IST                                                                      | Instituto Superior Técnico                                                                                                                                                                                                                                           |

| LDO                                                                      | Low-dropout regulator                                                                                                                                                                                                                                                |

| LED                                                                      | Light Emitting Device                                                                                                                                                                                                                                                |

|                                                                          | Lithium Cobalt Oxide                                                                                                                                                                                                                                                 |

| LiFePO <sub>4</sub>                                                      | Lithium Iron Phosphate                                                                                                                                                                                                                                               |

| LiPO                                                                     | Lithium-Ion Polymer                                                                                                                                                                                                                                                  |

| MPU                                                                      | Microprocessor Unit                                                                                                                                                                                                                                                  |

| ΝΤΟ                                                                      | Negative Temperature Coefficient thermistor                                                                                                                                                                                                                          |

| OCV                                                                      | Open Circuit Voltage                                                                                                                                                                                                                                                 |

| РСВ                                                                      | Printed Circuit Board                                                                                                                                                                                                                                                |

| Projecto FST                                                             | Projecto Formula Student Técnico                                                                                                                                                                                                                                     |

|                                                                          |                                                                                                                                                                                                                                                                      |

| PWM                                                                      | Pulse-Width Modulation                                                                                                                                                                                                                                               |

| PWM<br>RTCC                                                              | Pulse-Width Modulation<br>Real Time Clock & Calendar                                                                                                                                                                                                                 |

|                                                                          |                                                                                                                                                                                                                                                                      |

| RTCC                                                                     | Real Time Clock & Calendar                                                                                                                                                                                                                                           |

| RTCC<br>RTOS                                                             | Real Time Clock & Calendar<br>Real Time Operating System                                                                                                                                                                                                             |

| RTCC<br>RTOS<br>SAE                                                      | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers                                                                                                                                                                          |

| RTCC<br>RTOS<br>SAE<br>SD card                                           | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card                                                                                                                                                   |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD                                    | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device                                                                                                                         |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD<br>SoC                             | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device<br>State of Charge                                                                                                      |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD<br>SoC<br>SoH                      | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device<br>State of Charge<br>State of Health                                                                                   |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD<br>SoC<br>SoH<br>SPI               | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device<br>State of Charge<br>State of Health<br>Serial Peripheral Interface                                                    |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD<br>SoC<br>SoH<br>SPI<br>TS         | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device<br>State of Charge<br>State of Health<br>Serial Peripheral Interface<br>Tractive System                                 |

| RTCC<br>RTOS<br>SAE<br>SD card<br>SMD<br>SoC<br>SoH<br>SPI<br>TS<br>TSAL | Real Time Clock & Calendar<br>Real Time Operating System<br>Society of Automotive Engineers<br>Secure Digital Card<br>Surface Mounted Device<br>State of Charge<br>State of Health<br>Serial Peripheral Interface<br>Tractive System<br>Tractive System Active Light |

# Symbols

| Capacity                                             |

|------------------------------------------------------|

| Balancing current                                    |

| Load current                                         |

| Measurement current                                  |

| Busbar resistance                                    |

| contact resistance                                   |

| Internal resistance of cell / battery                |

| Load resistance                                      |

| Self-discharge current                               |

| Self-discharge rate                                  |

| Maximum cell voltage                                 |

| Minimum cell voltage                                 |

| Voltage drop through a contact                       |

| Measured voltage                                     |

| Voltage polarization of a cell through (dis)charging |

| Cell real voltage (Open Circuit Voltage (OCV))       |

|                                                      |

### Chapter 1

### Introduction

Electric propulsion is arguably the foremost green propulsion technology and despite its current drawbacks it's a fast becoming alternative against conventional powertrains. The battery is still one of the most limiting systems in any Electric Vehicle (EV), but there has been huge improvements in this area, especially regarding the advances in lithium battery technology which is why there have been increasing success cases of battery powered vehicles. These batteries yield a large increment in energy density mitigating two of the greatest shortcomings of EVs: the short range and poor performance. This advance comes with a drawback given the higher maintenance and safety concerns with this type of cells.

In fact this technology is dangerous enough that, even after more than two decades in the market and lots of progress and innovations in products from cellphones and laptops to EVs and planes, there are still reports of dangerous accidents and difficult to extinguish fires in such systems. Three *Tesla Model S* cars burning last year in less than two months [Green Car Reports, 2013] and two fires aboard the relatively new *Boeing 787* [Wikipedia, 2014], are a testament to the general danger of this cell chemistry. Still, it's no surprise that especially for competition purposes, this is the chemistry of choice for Formula Student (FS) competitions. Here EVs compete side by side with internal combustion prototypes and already claim the best positions all around in the latter years.

This thesis is made in a partnership with one of these teams — Projecto Formula Student Técnico (Projecto FST), from Instituto Superior Técnico (IST) — with the goal of rehabilitating its last prototype's battery and building the technology for future cars developing the required systems in-house. These prototypes are destined to compete in events organized by several engineers societies such as the Society of Automotive Engineers (SAE) or the Institution of Mechanical Engineers (IMechE), targeted at student teams from universities from the whole world. These competitions put the teams to the test in designing and building a formula car prototype against a set of rules, actual on-track performance, and all the management and business side of developing such project.

The dynamic events these prototypes run range from a short straight line (acceleration event) to a narrow and demanding track in which the cars have to run a total of 22 km (endurance event). For such electric car, the battery has to have a high capacity and voltage, increasing the dangers associated with any battery. One of the most important aspects in these batteries is therefore the monitoring system which assures the correct operation of the batteries, keeping them within their normal operation limits.

In particular, a Battery Management System (BMS) has the objective of monitoring voltage and temperature for a cell or group of cells. Usually, it also enables the safe recharging and discharging of the monitored cells within safe limits. Such systems are able to take preventive actions and avoid permanent damage to the battery or any surrounding system. For the purpose of this thesis, a BMS system comprises all of these functions since they are all needed for the intended application.

Figure 1.1: FST-05e and team in Germany 2013. [Courtesy of Projecto FST]

#### 1.1 Motivation

In 2013 Projecto FST went to three competitions but faced too many difficulties in several fronts that prevented the fifth prototype from running. One such difficulty was with the then new BMS system which failed to monitor the battery well enough. For that reason, the team decided to redesign the BMS for the next car, but having *FST-05e* rehabilitation as a milestone in the process. This would allow the prototype to have its official on-track debut in Silverstone, United Kingdom, in July 2014, and have the new battery system well positioned for the 2015 season with *FST-06e*.

The main shortcomings of this previous BMS design were mainly due to delays and consequential lack of testing, but also from design options that were proven to be flawed or not fully developed. Specifically, the voltage measurements in this system were dependent on individual calibration for each of the 144 channels in the whole battery and was still subject to big drifts in measurements. For that reason the team was always unsure of the real state of the batteries and the usable capacity of the battery was severely harmed from the increased restrictions we had to set in the BMS software.

The late delivery was also a problem that ultimately led to the software component never being fully developed. By the end of the 2013 competitions the system was merely a short lived "tech demo", and one that was proven unfit for the application.

From here arose the necessity of a new system that traded some of the previous features and design options for reliability, ease and speed of implementation.

While there are commercially available solutions, adopting those would restrict the ownership and fine control the team demands from such system, for both packaging and feature reasons. There is however an open hardware BMS: BMSafe [Poly eRacing, 2011]. Unfortunately, to date, it makes use of tools and hardware with which the team is unfamiliar, it's poorly documented and it has a significant lack of features. More importantly though, it's unmaintained (publicly) for two years and there is no performance data available.

It was then necessary to develop a custom BMS that was able to satisfy the team's specifications. Given the architecture always relying on a master module and the previous master module being sufficient to comply with the rules, a plan was worked out with the team to invest in the slave modules until the 2014 competition and limit the master functionality to what was already present in previous hardware.

Figure 1.2: FST-06e render for Class 2 competition in Silverstone 2014. [Courtesy of Projecto FST]

The master module could still make use of new features, that being the reason it was still redesigned in a later process even though most of the software was already functional with the previous one, minimizing the risk of developing such system.

#### **1.2** Project scope and objective

The objective of this work is the development of an all new BMS to replace the previous generation in the current and second electric prototype, *FST-05e*, and set a clear road towards implementation in future ones, specifically the *FST-06e*.

This thesis started from identifying any fault or shortcoming with the previous hardware, software and container combination in FST-05e to pin-point where the focus of the new work should be. This encompasses the new BMS (subject of this thesis) and the battery container as well.

The main objectives until July (Silverstone competition with *FST-05e*, *FSUK2014*) were therefore to investigate the appropriate specifications and design a slave module that would fit them. At the same time, the software should integrate these new slaves with the previous master module. This way, rather than designing a full system upfront, the new master module hardware could be delayed until after the competition with greater care put into the slaves and the software integration.

Also, all the control and safety features predicted in Formula SAE (FSAE) 2014 rules [SAE, 2014] and / or necessary for the safety of the system and to comply with the team's goals should be well implemented and tested before the competition. This includes some peripherals such as an interface that exposes all voltages and temperatures in a safe manner.

From this point, new features that weren't possible to develop before July — because of time constraints but also because of inherent limitations with FST-05e — should then be developed targeting integration in FST-06e. The sixth prototype is scheduled for completion early 2015, and by the end of 2014 this work should be ready to be relayed on the electronics and propulsion team of Projecto FST. Therefore, good and throughout documentation should also be provided. Given the calendar of this thesis, this work is only partially covered here.

Time on track being as valuable as it is, design should focus primarily on critical features. Phasing in

the system for early integration and testing is a main focus of this work.

Finally, the system should not significantly increase the cost of previous ones. The best appropriate reference being roughly  $1100 \in$  for the complete BMS system<sup>1</sup> with spare parts but without labor and cable harness from the *FST-04e* prototype [Guedes, 2011].

With this approach, and the tools developed, the new BMS should provide a future proof solution for a broad range of battery configurations. Additionally, a unified code base and hardware development should yield a greater maintainability and longevity of the prototypes with great benefits to design iterations.

All the developed hardware and software referenced throughout this document are hosted at https://bitbucket.org/projectofst with the prefixes *FST BMS* and *FST CAN tools*. All sources are distributed under a GNU GPLv2 license.

#### **1.3** System definition

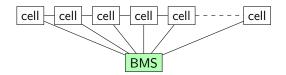

This work consists on the development and assembly of all the required modules to manage the battery pack(s). These include a module responsible for taking measurements and ensuring the correct balancing strategy to keep the cells working within their limits, but also to maximize the available capacity of the whole pack — these will be called *slave* modules from this point onwards. In *FST-05e* there are 6 stacks of 24 cells in series and 2 in parallel, requiring a total of 144 voltage measuring points, and in *FST-06e* there will be 12 stacks of 12 cells in series, a compromise should then be made in regard to the chosen architecture and how many measuring points each slave should have.

To manage the slave modules, a *master* module is required. Also, the master has the ability and duty of managing a set of relays that control the availability of high power to the Tractive System (TS), and a soft charge and discharge of the capacitors within the motor controllers. Finally, this module is responsible for all the communications with the exterior of the battery, from which everything else needs to be galvanically isolated.

In *FST-05e* there's only one battery container, but the team requires this container to be divided in two for the next prototype. This means that the system should support more than one master module, each with its own responsibilities within the respective battery container and the car. This increases the complexity of the system and care should be taken to keep one master from overruling the other or taking action without mutual agreement, depending on the task.

Each module, both slaves and masters, is a programmable unit that communicates in a dedicated Controller Area Network (CAN) network, with the master(s) being the only module(s) with access to an external CAN bus providing an isolated interface to the battery. This second CAN bus allows communications with a Graphical User Interface (GUI) running on a computer and with a *charger* module, responsible for the control of a stock racket 3 kW power supply to charge the battery.

#### 1.4 Structure of the thesis

This thesis is divided in eight chapters, the introduction being the first one. The remaining document follows the structure:

◊ Chapter 2:

<sup>&</sup>lt;sup>1</sup> Actual complete system with cells and container is necessarily more expensive given the technology being targeted. Throughout this work, cost will refer only to the BMS system.

Technical aspects of a BMS in general. Summary of the available technologies and their purposes.

There's also a brief overview of solutions from other formula student teams.

♦ Chapter 3:

An in-depth analysis of the the problems requiring a solution and specifications for the proposed BMS. The desired architecture of the BMS system, its peripheral modules and interfaces are discussed as well.

◊ Chapters 4 and 5:

On-board system (slave and master) is detailed, both the hardware and the software as well as details on some compromises being made.

◊ Chapter 6:

A set of tools required to debug and otherwise interface with the battery from a computer is introduced.

♦ Chapter 7:

Details on the actual usage of the system in laboratory and on-track.

◊ Chapter 8:

Final considerations regarding the chosen design, evaluation of attained objectives and description of possible / necessary future work.

### Chapter 2

### State of the art

BMS systems have existed for a long time with different purposes depending on the cell chemistry in use and the configuration of the monitored pack. Many batteries don't even need a monitoring system on-board for their inherent safety such as lead-acid batteries, even though chargers and "fuel gauges" or meters are often needed to fully maximize their potential.

The currently optimal chemistry for this project is a variant of Lithium-Ion Polymer (LiPO), given the higher energy densities and C rates<sup>1</sup> when compared with other allowed battery technologies by FSAE. All of the following sections will assume this chemistry when referring to batteries unless noted otherwise.

Therefore, the next sections provide an overview of this particular type of batteries and insight on the available BMS technology. Still it's worth noting some or all of these systems are also relevant to some extent to other battery chemistries.

A more comprehensive overview of the state of the art in regard to batteries and BMS systems is presented for instance in Andrea [2010].

#### 2.1 Battery technology

Lithium-ion batteries have been in extensive use in small devices like cellphones and laptops for a long time, typical systems having less than ten cells. Bigger applications are also increasingly common such as recent consumer EVs — e.g. *Tesla Model S, Opel Ampera* or *Chevrolet Volt* [CHEVROLET, 2014; Opel, 2014; Tesla Motors, 2014]. In fact, lithium-ion batteries are rapidly becoming standard in all sorts of consumer applications following as well as driving the reduced costs of fabrication.

These cells provide great energy densities, especially LiPO cells which replace the hard shell by a soft pouch with a polymer separator between the electrodes, thus reducing the weight<sup>2</sup>. Moreover, lithium based batteries have some of the lowest self discharge rates, i.e. the rate at which a cell looses charge in storage conditions.

Projecto FST wanted a competitive car with a demanding target weight of 200 kg for *FST-05e* and even stricter for *FST-06e*, therefore all considered cells are LiPO variants (see figure 2.1b). These come with a cost premium attached though, but as stated before lessened by the generalized demand and improved production

<sup>&</sup>lt;sup>1</sup> The charge and discharge rate at which the cell may be used safely. For instance, for a C=5 A h, a cell rated at 20C nominal discharge can withstand a discharge of  $20 \times 5 = 100$  A continuously.

<sup>&</sup>lt;sup>2</sup> Another kind of lithium polymer cells, not to be confused with LiPO, actually have a polymer (solid) electrolyte, but those have currently issues that prevent their introduction in the market. In this document, LiPO denotes the first kind of cells, not the second.

(a) Headway 38120S cylindrical lithium-ion cell, as used in FST-04e (120×38mm).

(b) EPS4500XP LiPO (pouch) cell, as used in FST-05e (152×44mm).

Figure 2.1: Two types of lithium-ion cells. Not to scale.

#### processes.

These cells are structurally prone to damage with the delamination of the electrodes from the polymer sheet, increasing internal resistance and reducing capacity. Besides, physical damage is also associated with some cases of swelling and spillage of the electrolyte. For this reason, LiPO cells have greater packaging issues, but the saved weight and volume is nonetheless important for small applications like cellphones and high performance applications in general.

These are currently some of the most challenging batteries to manage for their sensitivity to overcharges, deep discharges and temperature issues, making them a primary target of BMS manufacturers. Actually these cells are famous for their thermal runaways usually resulting in explosions and / or hard to extinguish fires. These malfunctions are often times caused by physical abuse, but also from overcurrents and overcharging.

Additionally, cells overly discharged rarely accept energy again, effectively becoming unusable — note however that the residual energy required at all times to avoid this is not part of the stated capacity, not counting towards the energy density calculations.

Depending on the composition, LiPO cells have slight variations of nominal voltage, capacity and C rates, but large variations of degradation rates and inherent safety. The best performing chemistries sacrifice lifespan and safety for larger C rates and capacity, but new fabrication processes are constantly pushing these limits. Still, all of them pose the same problems regarding the required BMS features to manage such batteries and the differences are usually small enough that a single BMS model is able to accommodate all chemistries.

One of the highest performing chemistry is Lithium Cobalt Oxide ( $LiCoO_2$ ), being the chosen technology for *FST-05e* and *FST-06e* over the safer yet more limited Lithium Iron Phosphate ( $LiFePO_4$ ) used in *FST-04e*. These offer the best energy densities and C rates of the lithium-ion family, and are the main target of the proposed BMS system.

#### 2.2 BMS features

BMS systems have a huge range of functionalities and may implement those in different ways. The first distinction to be made is between analogue and digital BMSs.

The superior and most common option is digital, which allows easier (re)configuration and integration, besides the collection of invaluable data to be recorded and / or transmitted to other interfaces. Additionally, if there is a fault within the battery, a well designed digital BMS is capable of identifying where the fault was detected (e.g. which cell is above some threshold) and by how much (e.g. by how many volts the cell is above its limit). Another important feature of digital BMSs is the ability to report the level of charge still available from the battery, usually an important feature of any battery powered device.

In contrast, an analogue system may identify every fault but is typically very limited in informing the user or a peripheral module of which fault occurred, where and by how much. On top of that, changing a configuration (e.g. adjusting the overvoltage threshold) is a hardware adjustment that has to be made individually for each channel.

Analogue chargers / balancers (a form of BMS) are still of great importance in standalone chargers for cylindric cells for instance. These devices are often targeted at a specific chemistry or use a selectable preset for each one, being generally cheaper than equivalent digital chargers. Still, LiPO cells demand that a BMS is present at all times and not only for charging. It's no surprise then that analogue BMSs are not that common for LiPO cells.

Finally, among both categories there are a few kinds of BMS systems beside cell balancers, each with different features as seen in table 2.1.

| BMS type           | Balances cells | Requests that<br>battery be<br>switched off | Capable of<br>shutting down<br>battery | Reports<br>individual cell<br>voltages, etc. |

|--------------------|----------------|---------------------------------------------|----------------------------------------|----------------------------------------------|

| Protector          | $\checkmark$   | $\checkmark$                                | $\checkmark$                           | $\checkmark$                                 |

| Balancer           | $\checkmark$   | $\checkmark$                                |                                        | $\checkmark$                                 |

| Monitor            |                | $\checkmark$                                |                                        | $\checkmark$                                 |

| Meter / Fuel gauge |                |                                             |                                        | $\checkmark$                                 |

Table 2.1: Distinction between BMS types; red column only applies to digital BMSs.

A complete LiPO BMS system offers all of the summarized features, as it is usually the case with cell packs that are sold as a final assembled product. However, there's a huge need for custom specifications, for which reason there are BMSs that only offer certain features leaving others to be supplemented by the buyer through their own systems.

An example where such BMS would be required is when the user needs to comply with certain unconventional regulations that wouldn't be supported by a complete commercial solution — e.g. FS competition rules.

#### 2.2.1 Cell balancing

Batteries are often a set of individual cells connected in series and parallel to achieve the required voltage and capacity. Whenever there are more than one cell in series, the battery may become unbalanced, i.e. different cells may have different charge levels. Assuming cells with  $V_{min}$ =3.0 V and  $V_{max}$ =4.2 V, figure 2.2 illustrates a possible scenario of a battery charged to its fullest, yet well below its full capacity.

```

Figure 2.2: Example of an unbalanced array of cells.

```

This illustrates how a single cell in series hampers the ability to extract or store the nominal energy of the pack. The whole battery is 100 % discharged or charged whenever a single cell in series reaches its lower or upper voltage limit. With severe unbalancing of a battery, the actual usable capacity may be reduced to very low levels even if the cells themselves are in good conditions and performing within their specified limits. An extreme case would be a battery 100 % charged *and* discharged at the same time, not allowing any current in or out without risking permanent damage.

The reasons why a battery becomes unbalanced are differences in capacity and self discharge rate. These are usually very abrupt between different chemistries and manufacturers obviously, being one of the reasons why different cells shouldn't be used within the same system. Still, that's an avoidable problem, but even cells of the same model and from the same manufacturer are bound to have slight differences. Given enough time, these differences pose a balancing problem regardless of being actually common for manufacturers to match cells before shipping them.

Cell wear is another mechanism to unbalance a battery even further with the associated increased internal resistance and lower capacity. For a large battery it's not cost effective to throw all the cells away whenever a single one shows signs of wear. However, mixing older cells with new ones is equally bad for the battery even if it isn't damaging in any way to the cells as it would be in connecting them in parallel without being closely matched.

Furthermore, lithium-ion cells in particular age faster at certain voltage levels than others. Most suppliers recommend a minimum charge of 40 % for storage. Severe unbalancing may then contribute for a faster aging and degradation of the whole pack and the least charged cells in particular.

The balancing issue is therefore the reason why a BMS should have, or 'must' in the case of LiPO cells, ways of assessing each cell voltage individually. Leaving a single cell unmonitored means it could be completely unbalanced against the others and could lead to permanent damage to that cell or even the whole accumulator with potentially dangerous consequences.

To cope with cell wear and balancing problems in general, several mechanisms exist, some more sophisticated than others. An example of an advanced system would be a grid capable of taking one cell or group of cells offline, effectively emulating the action of disassembling a battery and removing the problematic cells. While these systems are the only option to deal with damaged cells without interrupting the power supply, they're not the ideal solution to balance cells, even more because of the infrastructure these systems require, making them only usable in stationary batteries where size and weight is not a concern.

To properly handle cell balancing though, there are two approaches: wasting excessive energy in cells that are more charged than the others and transferring energy from the most charged ones to the less charged. These techniques are often called *passive* and *active* balancing respectively, or *dissipative* and *non-dissipative*. The differences between the two are analyzed in the following subsections.

Common to both solutions though is the balancing effort required by a system: how much energy should be moved around or dissipated to keep a battery balanced? The answer to this question is part of the BMS system specifications and will be discussed in chapter 3.

#### 2.2.1.1 Passive balancing

Passive balancing is based on the dissipation of energy, usually in the form of heat through resistors. This requires that the governing BMS identifies cells with more charge and connects them individually to a resistor or group of resistors until their charge is back within a certain difference to the least charged one. The result is a battery with lower charge yet capable of subsequently storing more charge than if only a single cell reached the upper limit instead of all of them.

While it's arguably wrong to waste energy from an environmental stand point, this solution is still better than producing and recycling batteries. Therefore, the greatest disadvantage is not the environmental impact but the heat dissipation, or lack thereof. In fact, the heat generated by such system may be harmful to cells, BMSs and even the resistors responsible for this dissipation.

However, this balancing strategy is easier to develop and implement, and cheaper since it uses only passive components like resistors. Also, the BMS may not have any extra connection to the cells since the voltage sensing connections may be used for balancing purposes. Finally, the added volume and weight required for the refrigeration systems (when needed) aren't meaningful compared to the volume and weight required by active solutions.

#### 2.2.1.2 Active balancing

This solution is by far the most complex and there are several ways to achieve it. The short term advantage is that it moves energy around through Direct current (DC) to DC converters (DC/DCs) instead of dissipating all that energy.

This characteristic is very important in certain EV applications allowing, for instance, a car to be parked for a few hours and have a boost in available energy once the owner returns, without any actual charging of the vehicle. This is due to the BMS usually shutting down the battery once the first cell is depleted or nearly so. Since the least charged cells receive some energy from the most charged ones, this results in an increased available capacity despite actual stored energy being obviously lower by the end of the balancing process.

Also obvious, this process takes time, so for instance if the EV in question is not a convenience vehicle and has no down times between cycles, this system may not yield any advantage from a usability point of view since it won't balance the batteries quickly enough, as discussed later. That wouldn't take away the advantages in the charging process and thermal management though.

The main disadvantages of these solutions are the price, the increased development difficulty, as well as the complex cable harness and extra peripheral devices that most of these systems require. Also, these systems aren't usually very efficient as a whole as their efficiency is highly conditional on the battery state, with actual balancing capabilities being very moderate. This may be circumvented with larger systems, but again at the cost of extra volume, weight and price.

There are three common configurations for active balancing systems: cell-to-battery, battery-to-cell and bidirectional. As the name implies, the difference is in the way energy is transferred from some cells to others, each allowing for several topologies with varying numbers of converters and switches.

Another alternative is a cell-to-cell mechanism, the usual implementations having cells feeding adjacent ones. This is easily the cheapest and smallest solution, but unfortunately it's only capable of very small balancing currents and has low efficiency. An overview of this and other mentioned configurations is shown in table 2.2.

However, despite passive and active balancing being concurrent features, the compromise in a battery design is not between the chosen balancing technique — unless the judgment is strictly environmental of course. It's rather a compromise between active balancing and increased battery capacity, since that's the

| Converter     | <b>Cell-to-battery</b><br>Low to high voltage.                                                                                                                                                     | Battery-to-cell<br>High to low voltage                                                                                           | Bidirectional<br>Bidirectional                                             |                                                                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation     | Feeds the battery when a cell is excessively charged.                                                                                                                                              | Feeds a low capacity cell when battery is sufficiently charged.                                                                  | Feeds the I<br>depending or<br>cha                                         | Feeds the battery or the cells A cell feeds adjacent ones if more depending on ratio of excessively charged, else is fed by adjacent charged cells. cells.                                         |

| Advantages    | <ul> <li>Very efficient.</li> <li>Switches are on the low voltage<br/>side.</li> <li>Most effective when only a<br/>minority of the cells have low<br/>charge (most converters active).</li> </ul> | ♦ Most effective when most cells<br>have a low charge (most<br>converters active).                                               | ♦ Effection towards                                                        | <ul> <li>◇ Effective regardless of bias</li> <li>◇ Small low voltage components.</li> <li>towards most cells charged or</li> <li>◇ Easy integration within the uncharged.</li> <li>BMS.</li> </ul> |

| Disadvantages | $\diamond$ Bad efficiency $/$ cost ratio.                                                                                                                                                          | <ul> <li>◇ Bad efficiency / cost ratio.</li> <li>◇ Requires high voltage switches<br/>and isolated control circuitry.</li> </ul> | <ul> <li>◇ Bad effi</li> <li>◇ Most com</li> <li>switches chigh</li> </ul> | <ul> <li>◇ Bad efficiency / cost ratio.</li> <li>◇ Most complex solution: requires<br/>switches on both the low and<br/>high voltage side.</li> </ul>                                              |

Table 2.2: Comparison of active balancing strategies in usual topologies. Actual implementations introduce some variations tough.

advantage of this system.

In certain applications the available capacity is greatly increased with active balancing as in the car example mentioned earlier, but other applications may present a situation where adding extra cells to the battery is more cost, weight and/or volume effective, with different applications prioritizing different performance parameters.

Such an example is given in Andrea [2010] for an application where the only performance measure is price. The conclusion being that it's not cost effective to invest in active balancing if the battery is depleted in less than 20 minutes. This evaluation is derived from the average dollar per Watt cost of converters and dollar per Watt-hour cost of lithium batteries from 2010.

#### 2.2.2 Performance parameters

There are three parameters usually determined for batteries: State of Charge (SoC), Depth of Discharge (DoD) and State of Health (SoH). These have different aims at providing information of how much 'fuel' is left and general health of a battery.

These parameters are determined in several ways, but some are not possible to use depending on chemistries and some even being destructive to the cell. For common purposes, on a live system, these are important performance indicators nevertheless, and several indirect ways of determining these parameters are possible. In this work, the methods of interest are those capable of working in live systems, particularly taking advantage of a digital BMS.

For lithium-ion cells, the indirect ways of determining them rely on measurements of voltage, current and temperature, but SoC, DoD and SoH have a very non-linear and interdependent relation with these and many other factors. In order to correlate these with the intended parameters, voltage measurements, current integration (Coulomb counting), self-learning algorithms, modeling and others or a combination of them are used. Extensive examples and analysis of most common methods are found in Pop et al. [2008] and Bergveld [2001] to name a few.

#### 2.2.2.1 SoC and DoD

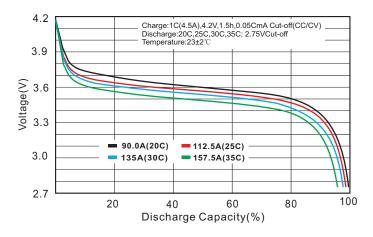

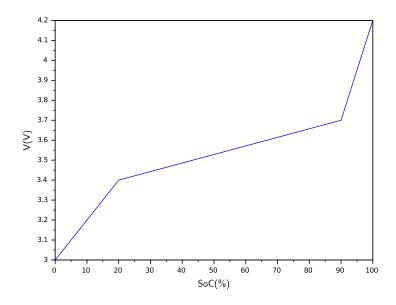

SoC is usually intended as a percentage of available charge in a cell or cell pack from 0% to 100%. For certain battery types, this poses no challenge as charge varies somewhat linearly with the voltage, but lithium-ion have a very non-linear relation between the two — see figure 2.3. The problem is actually worse since temperature, usage history and several other factors may have great influences in perceived voltage for any charge level.

"Theoretical [SoC] calculations are based on Coulomb counting modified by the cell voltage and temperature, the rate at which cells have been charged and discharged, the chemical composition of the various active chemicals and any doping which has been used, the possibility and effects of contamination, the shape and length of the physical current paths within the cell, the volume of electrolyte, the thickness of the electrolyte and the separator, the resistivity of the components, the rate of mass transfer of the ions through the electrolyte, the rate of chemical action at the surface of the electrodes or the rate of absorption of the ions into the intercalation layers, the actual surface area of the electrodes, the effect of passivation on the electrode surface, the ambient temperature, the Joule heating effect, the self discharge rate of the cells, the time between charges plus possibly several other factors."

— Electropaedia [2014]

Figure 2.3: Discharge rate characteristics for LiPO cells EPS4500XP, used in *FST-05e*. [E Propulsion Systems, 2012]

As the quote suggests, even with a lot of parameters and measurements known for any given cell, a purely theoretical and universal approach is nearly impossible. However, for a lithium-ion cell, there are two SoC values possible to identify with 100 % accuracy in a very easy way: when its voltage reaches the lower or upper bound.

These bounds do not mean the cell is as charged as it can be — i.e. maximum capacity —, it only means that the cell cannot be discharged or charged further without cycling it or risking damage to the cell, which fits the definition of SoC. However, even this presumes the cell is in open circuit (Open Circuit Voltage (OCV) measurement) and that it had enough resting time to eliminate influences from the polarization of the cell.

Fortunately, for  $LiCoO_2$  cells, Closed Circuit Voltage (CCV) differs only slightly from OCV, even for relatively high currents. This is due to the usually small internal resistance, but as a cell wears down this resistance may increase significantly. In such conditions, even a LiPO cell may be charged to its maximum of 4.2 V and some minutes or hours later, in open circuit, measure only 3.4 V, for instance.

The voltage difference may and should be modeled and accounted for, but a better method of avoiding such problem is to use Coulomb counting. This is a very common technique to cope with the problems of measuring accurate voltages and non-linearities between voltage and charge.

Finally, DoD is somewhat the opposite of the SoC giving a percentage of how much charge was already drained. Depending on the intention of the developer, DoD may go beyond 100% — e.g. if a cell has higher capacity than nominal rating and Coulomb counting is used to determine the value. However, regardless of the implementation, these are usually similar parameters that are calculated with similar methods.

Table 2.3 summarizes available methods for SoC and DoD determination of lithium-ion cells although they may apply to other types of batteries.

#### 2.2.2.2 SoH

A good SoH implementation should detect differences in cells, degradation relative to nominal characteristics and cells that have degraded unevenly since installation. The first applies to a battery whose performance is affected by using cells with dissimilar characteristics. An example of the second and third situations is a battery that has already made several full cycles and has consequently aged, evenly or not.

SoH determination may then need to be tuned to reject production margins. On the other hand, these

| Method                                       | Advantages                                                                                                        | Disadvantages                                                                                                                                                                                                                                 |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Discharge test                               | <ul> <li>◇ Accurate</li> <li>◇ Easy</li> <li>◇ Independent of SoH</li> </ul>                                      | <ul> <li>◇ Offline</li> <li>◇ Time intensive</li> <li>◇ Change of battery state</li> <li>◇ Loss of energy</li> </ul>                                                                                                                          |

| OCV                                          | <ul> <li>◇ Online</li> <li>◇ Easy</li> <li>◇ Cheap (it has to be provided for safety purposes already)</li> </ul> | <ul> <li>◇ Non-linearity</li> <li>◇ May require some rest time<br/>after charging or discharging</li> <li>◇ Demands high precision voltage<br/>measurements</li> </ul>                                                                        |

| Coulomb counting                             | <ul><li>♦ Online</li><li>♦ Accurate</li></ul>                                                                     | <ul> <li>◇ Requires several re-calibration<br/>points</li> <li>◇ Depends on initial state<br/>(integration problem)</li> <li>◇ Demands high precision current<br/>measurements</li> <li>◇ Very sensitive to parasite<br/>reactions</li> </ul> |

| Artificial neural<br>network                 | ◊ Online                                                                                                          | <ul> <li>◇ Requires training data from<br/>similar battery</li> <li>◇ Expensive development</li> </ul>                                                                                                                                        |

| Fuzzy logic                                  | ◊ Online                                                                                                          | ◊ Requires a lot of memory in<br>real-world application                                                                                                                                                                                       |

| Extended Kalman filter<br>(state of the art) | <ul> <li>◇ Online</li> <li>◇ Dynamically adapts to errors<br/>and SoH</li> </ul>                                  | <ul><li>◇ Difficult to implement</li><li>◇ Requires suitable battery model</li></ul>                                                                                                                                                          |

Table 2.3: SoC and DoD estimation methods for lithium-ion cells. [Piller et al., 2001; Pop et al., 2008]

production margins may be significant enough that should impact the "health measure" of a battery. This is only one of the arbitrary aspects in the definition of this parameter.

Actually, SoH is by far the most arbitrary of the three parameters mentioned. For a single cell, its health is tied to the actual capacity in relation to the nominal value and variations in internal resistance<sup>3</sup>. Each has different implications, yet these are still interconnected. Therefore, for a single cell, it's difficult to define a single expressive performance value of health.

Moreover, while one can easily argue how the SoC of a cell influences the SoC of the battery, it's not as easy to define how the health of one cell influences the health of the pack. For this reason, any SoH parameter may refer to the cells or the battery, but it's not possible for a single value evaluation of the health of both.

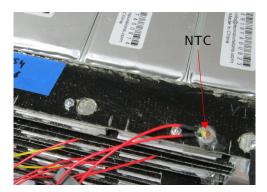

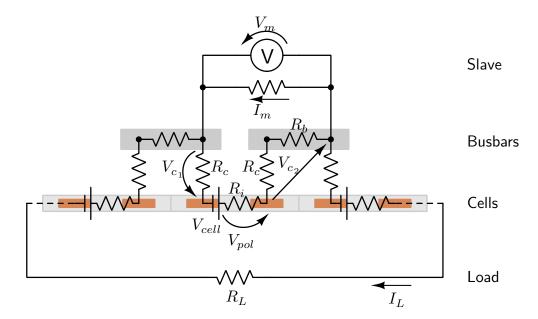

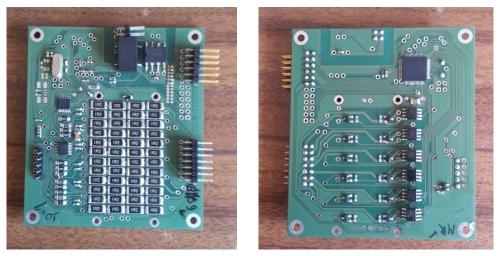

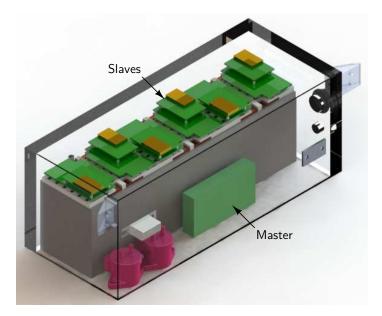

To evaluate the health of a battery, the available methods are somewhat similar to those of table 2.3. The difference is in the parameter and meaning extracted from the measurements, models and filters.